(原标题:最可能触发CPO switch的奇点是什么?(上)--TSMC的做了什么?带来了什么变化?)

原创 老牛爱骑电瓶车 电光夜谈

CPO是个大方向,这是业界广泛认可的事情,但是,什么时候会正式的规模商用,大家的观点还是比较离散的。要回答这个问题,我们就需要寻找一个恰当的观察点,判断什么是CPO switch的奇点,过了这个奇点,就是雪崩效应了,后面的事情就没有什么特别需要争议的地方了。今天,就从几个方面来聊一下这个事情。

首先从可插拔光模块说起。

一、可插拔光模块在DC网络互连的地位

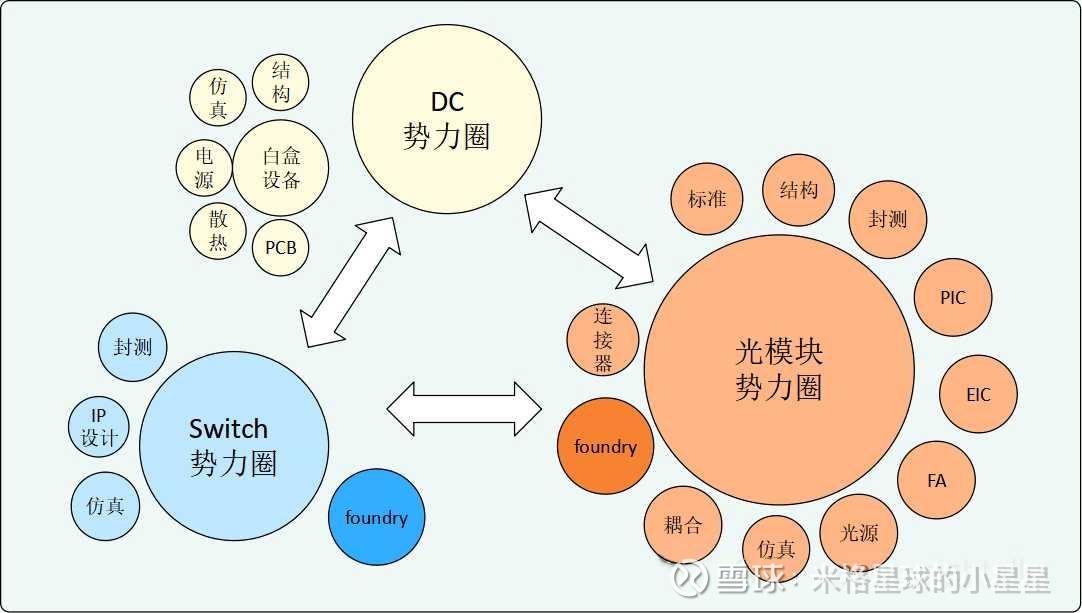

目前,DC配置光模块的白盒设备中,大概有70%-80%左右的成本来光模块,可见,光模块在整个产业链中的角色是举足轻重的。数据中心的通讯互连这块,可以说存在着三大势力圈,即DC用户、光模块厂家和switch公司。其它的元素,例如IP设计、仿真、pcb、测试、封测、光纤连接器、结构、白盒设备,foundry等等等,都是围绕这三大要素进行配套。形象的说法,在目前的DC中心互连网络市场就是,DC用户、光模块厂家和switch厂家的三国演义。非敌非友,相互共存,互相制约。

DC作为最终的用户,地位自然不用说,始终存在,不同的DC网络,会根据自己的网络需求,使用各自的方案,对光模块的牵引影响力更大一些。同时,也会根据行业的技术水平和能力进行方向调整。

switch作为一个技术的聚合点,尤其是其带宽需要在不同的制程下,通过不停的迭代来保持功耗和性能的优化,其地位也是难以撼动的,目前,业界能够跟上这个节奏起舞的,也就是那个,进入门槛非常高。

光模块厂家,作为独立的一个势力群,也是非常庞大的产业存在,销售规模庞大。

foundry在技术的复杂程度方面应该是很高的,但是,从目前的情况来看,foundry似乎扮演的份量不够,没有形成自己的独立路线,不同厂家的特色没有显示出来,也就是,其技术能力没有发挥到最大,也是最有前景的一个势力。这是一个话题,我们留到后面再来回答这个问题。

其它的元素,例如设备角色,曾经扮演过重要的角色,在白盒阶段逐渐失去话语权,沦为配角。

在CPO阶段,这个势力的演进图会有进一步的变化,后续再聊。

二、可插拔光模块的前世今生

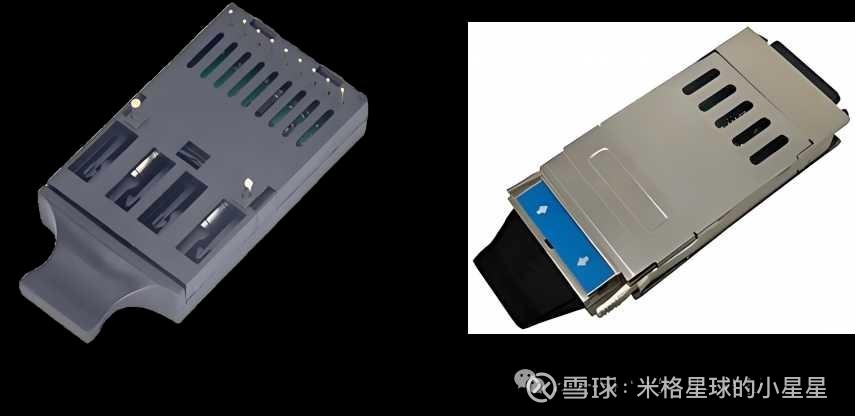

目前数据中心常用的可插拔光模块的前身是直接焊接在板子上的光模块,即下图所示的1*9封装的光模块。

由于焊接封装的模块存在故障定位、维护不方面的等因素,慢慢就出现了可插拔模块的需求,最早的时候应该是GBIC封装的。后来,运营商发现这个接口是标准化的,于是就开始了集采,这样可以降低成本,这种模块就一直延续到现在。

就是说,光模块最初的时候,是集成在线卡上的,由于其高故障率,再在最终用户的大力推动下,于是就形成了目前大家熟悉的商业模式。

三、可插拔光模块的存在的逻辑是什么

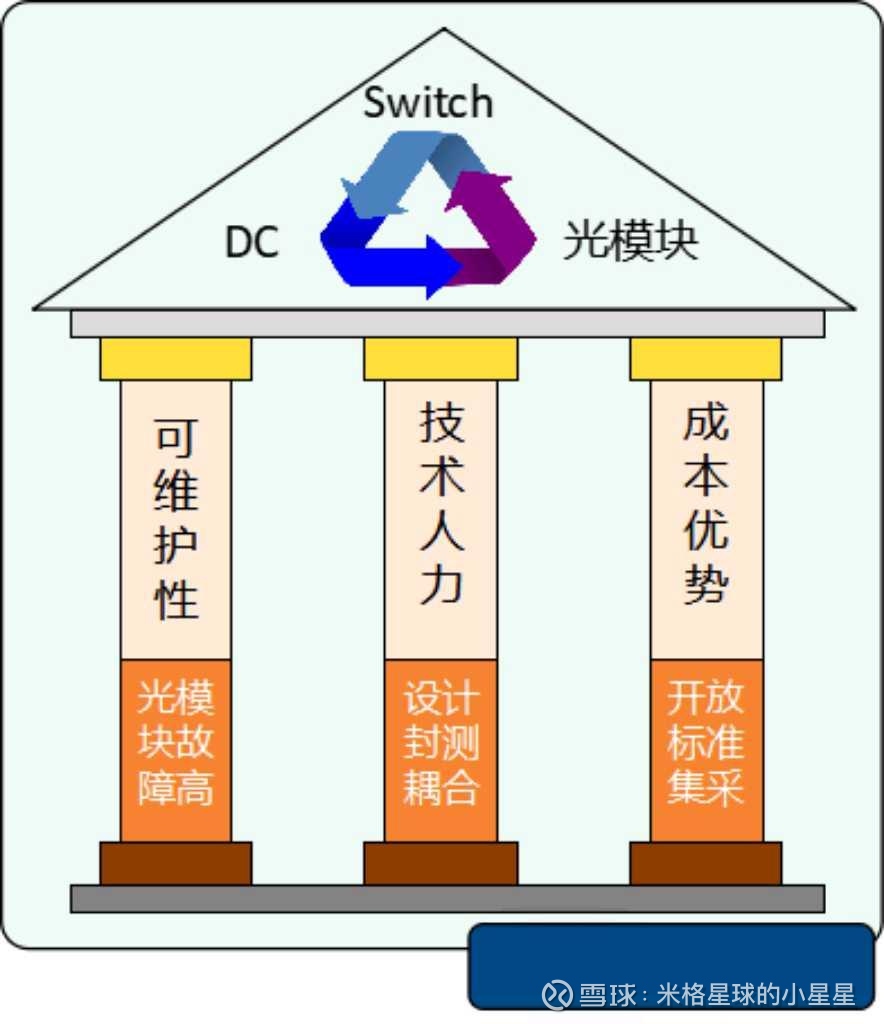

虽然,可插拔光模块在信号完整性,在热设计方面等并不是最优的,但是,可插拔光模块目前形成一个非常庞大的生态,肯定存在必然的逻辑。

首先,可插拔光模块的可靠性是低于CMOS器件的,即比主要的ASIC要更容易出故障,这点也是可插拔光模块最初的驱动力,目前来看,这个驱动力依然存在。在用户看来就是可维护性。

其次,随着光模块速率的上升,光模块本身的技术复杂度也在不断地提升,包括调制器、光源、芯片、封装、耦合和测试方面,形成一个复杂的技术和人力资源的综合体,这是光模块产业链本身存在的一个基本的技术资源逻辑。

最后,就是开放的标准,主要是和ASIC对接的接口的标准化,使得光模块能够和不同厂家的交换机进行解耦。最终形成光模块厂家之间竞争又共同促进的这样一个生态圈,最终实现成本和多元供应的优势。

简单的说来,正是通过这三大支撑,使得可插拔光模块能够在数据中心通讯网络市场中,和DC用户、switch厂家形成三足鼎立的格局。

从整体上来看,在上面的三大支柱中,和可插拔光模块厂家最直接相关就是可插拔光模块自身的技术门槛和由于需要大量人力进行耦合、测试等的生产性方面的门槛,如果这个门槛降低的话,可插拔模块的在整个数据中心供应链的生态中的话语权就会减弱,可能会演变为的设备厂家的角色。

四、TSMC做了什么?

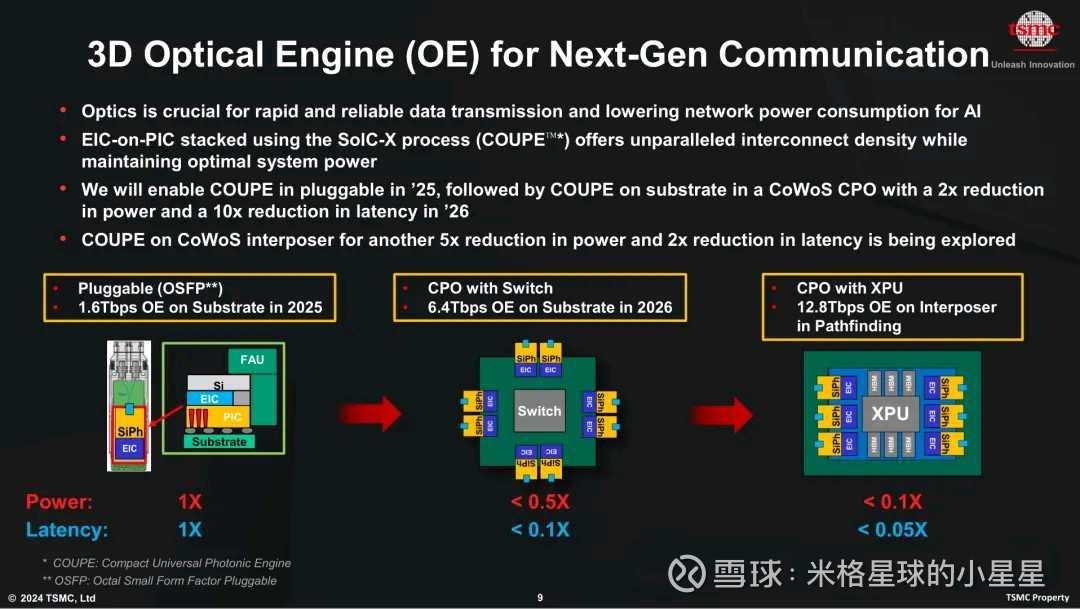

在2024年TSMC的北美技术论坛上,TSMC介绍了他们在CPO方面的一些工作,正式向公众公布了他们在CPO方面的研发的节奏。

我们来看看,TSMC具体做了些啥呢?

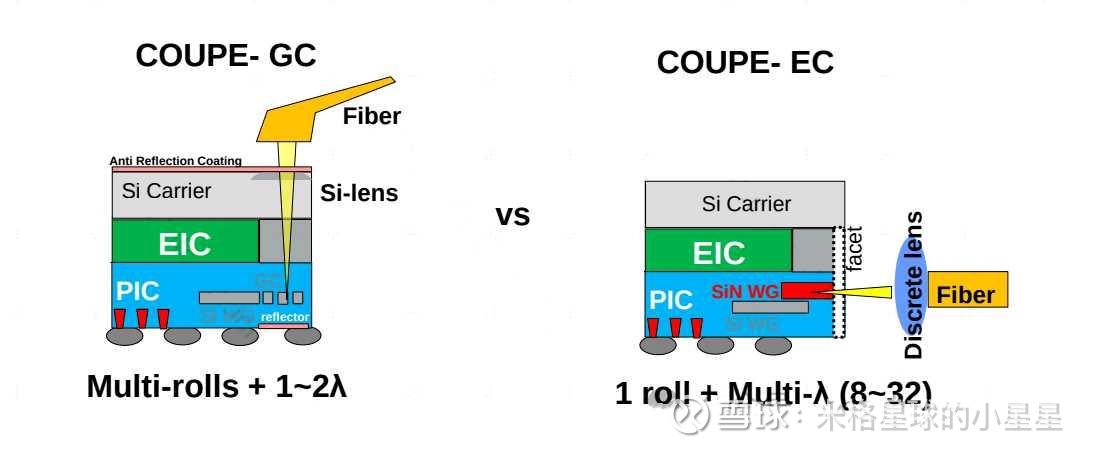

TSMC的硅光封装平台iOIS有两条线,一个是COPUE(Compact Universal Photonic Engine)2.0,一个CI(Composite Interposer)。COPUE 2.0又包括光栅耦合和EIC-PIC的铜铜键合两大块的内容。

1、耦合-光纤 re-attachable

对于硅光来说,PIC和光纤的耦合是一个非常麻烦的事情,光栅耦合面临带宽和插损的问题,水平耦合则需要复杂的对准的设备和人力,相对于乒乓球和篮球进行双向耦合,尽管上了各种手段,但是,还是存在耦合良率的问题,这也是可插拔光模块的一个人力门槛。如果能够实现光纤的可插拔/可拆卸,则是一个颠覆性的技术,彻底解决光纤耦合的难题。

目前的的光纤的可拆卸有四条路,一种是博通的方案,使用lens阵列进行光纤的可拆卸连接,这个方案对外面的结构件的精度要求比较高,在高密封装的时候,需要进行统一考虑。第二种方案以senko为代表,是在pic的出口处加上几路反射镜,扩斑进行耦合,这个方案对于安装精度的要求也是比较高,同时,路数如果多的话,误差积累比较大。即对耦合的数量也是有限制的。第三条路,是intel系,采用在玻璃上进行3D刻蚀,通过适配器将PIC上面的光扇出,这个方案存在飞秒激光的3D刻蚀,在刻蚀的时间、成本上可能会有问题,同时,还是需要有给玻璃和PIC耦合的过程。第四方案就是直接在PIC的晶圆上做文章,这一个是从根本上解决耦合的一种方式,目前看到的除了tsmc,还有就是teramount和IMEC的合作,通过微转印的方式来实现,容差高,可以达到±30um的精度,轻松实现光纤的可插拔,而且支持3D的高密度耦合。

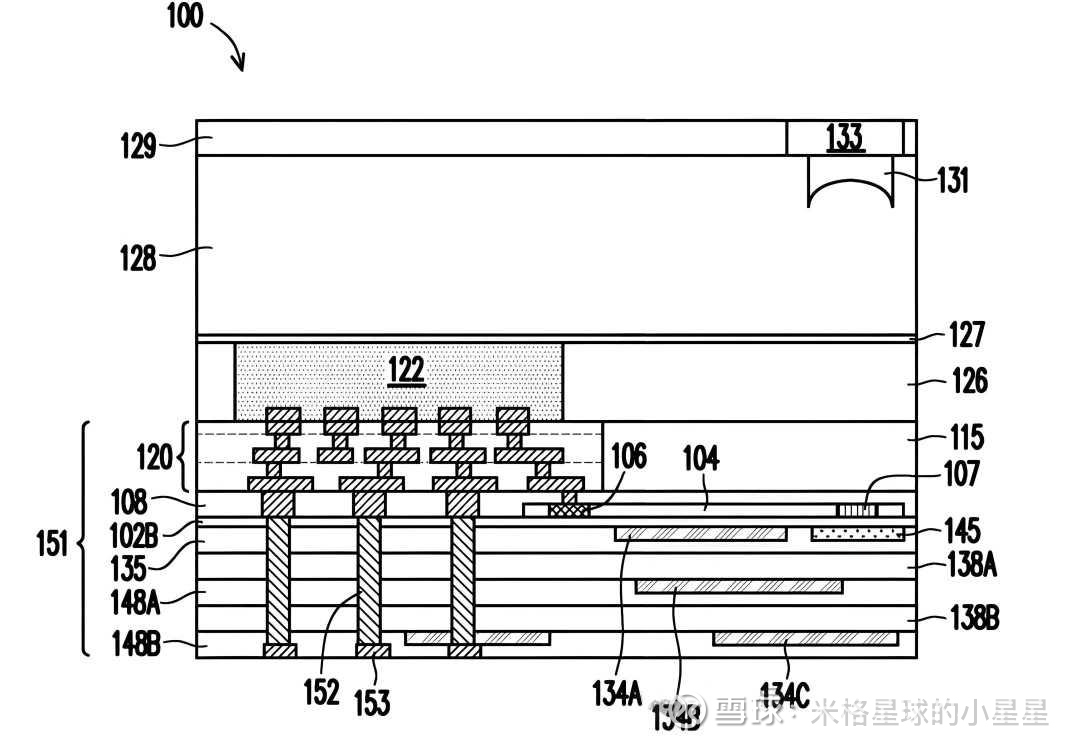

TSMC与微透镜结合的宽带光栅耦合器可以在COUPE2.0中实现,这是一种宽带光栅耦合器,该方案兼顾了光栅耦合器的灵活性以及边缘耦合器宽带工作的优势,耦合损耗可达0.3dB,对准容差为±10um,结合微透镜,对准容差可以扩大至±20um。实现光纤的可插拔/可拆卸足以应付了。其示意图如下图所示。

上面的四种方案种,都没有经过市场的规模验证,以台积电的口碑来说,应该是非常又前景的方案。

2、 EIC和PIC的混合键合

台积电将混合键合(hybrid bonding)的技术引入到COUPE2.0中,信号通过TSV进行垂直互联,PIC与EIC中间不再存在micro-bump,没有空隙,将寄生参数最小化,从而带来功耗的降低与性能的提升。

台积电的这项技术非常复杂,在混合键合中,铜 pad 建立在每个芯片的顶面上,铜被绝缘层(通常是氧化硅)所包围,pad 本身略微凹进绝缘层的表面。在对氧化物进行化学改性后,将两个芯片面对面压在一起,使每个凹陷的 pad 对齐。然后慢慢加热这个夹层,使铜膨胀到间隙处并熔合,从而连接两个芯片。需要在原子层面来控制凹进去的部分,凹多了结合力不够,凹少了会把晶圆推开。混合键合技术可以实现更高密度的电互联,其pitch可以小于20um。由于两片wafer间没有空隙,寄生参数非常小,可以支持更大的带宽。TSMC号称是业界唯一可以量产混合键合的公司,尽管有好几家业界顶尖的公司也在做。

混合键合的意义非常大,首先,对OE的单片集成(GF)形成非常大的压力,其在寄生参数方面的优势就大幅度的减小了,那么此时单片集成在EIC的工艺节点上的劣势就凸显出来了。其次,低寄生参数,意味着高速,意味着向后续的高速演讲就更加的平稳。最后,还可以充分利用OE的各组件在材料、制程工艺方面的优势,实现综合最优。

3、各种花式的封装板

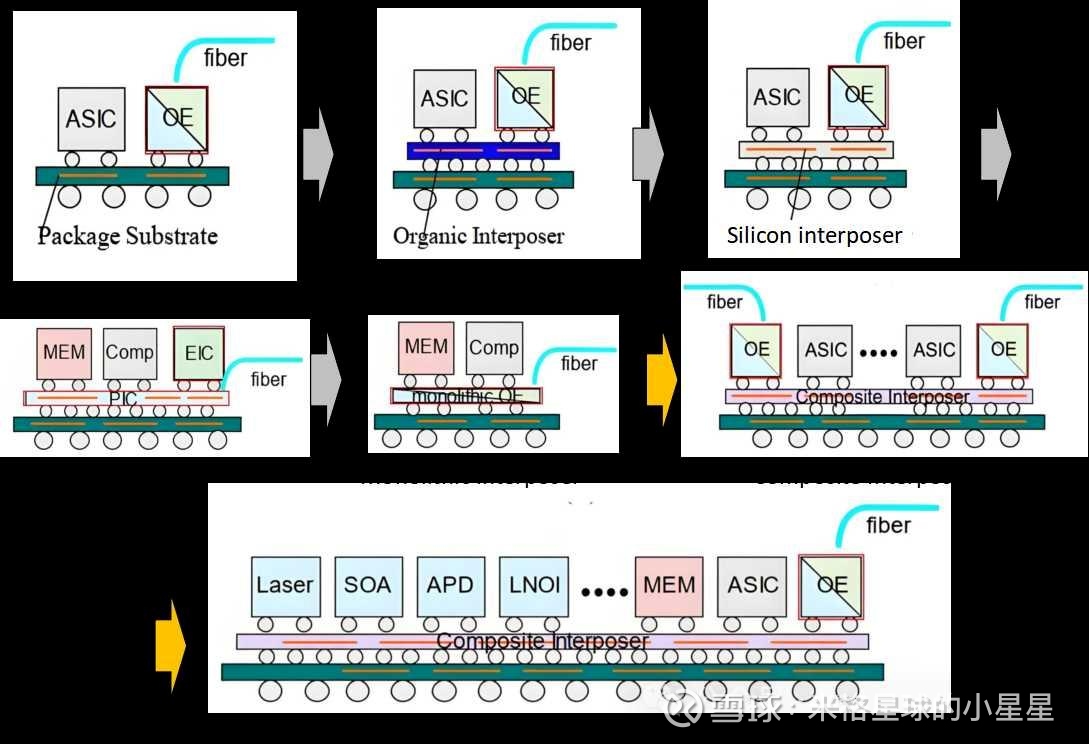

CI即(Composite Interposer),包括一系列的基板/中介板的封装形式,从封装基板->有机中介板->硅中介板(无源)->PIC中介板->OE中介板,再到各种TSMC惯用的花式组合,可以满足从简单到复杂的多种封装,这个是他们的老本行,玩得很溜。

TSMC的CI平台的全面的布局,意味着在全方位的介入光电共装的行业,从可插拔模块的组件,到linghtmatter的这种超级的算力单元实现了全覆盖。

4、介入硅光产业链势在必行

从TSMC的商业模式上来看,他们的边界还是非常清晰的,只做代工,不涉及到芯片的具体内容,但是,上面TSMC在光互连方面的布局来看,介入硅光的产业势在必行。

首先,光栅耦合是需要在PIC的设计层面进行设计和控制的,这也是从根本上解决光纤和PIC耦合的方案。也是要TSMC自己流片,或认证的公司来流片的。

其次:对于COUPE 2.0来说,如果EIC、PIC是第三方生产的,那么铜铜键合的良率基本上无法保障。就是说PIC必定自己生产,那么就需要把PDK开放给第三方,再有台积自己流片生产。

再次,对于各种interposer,尤其是后面的PIC中介板和OE中介板,如果TSMC不自己流片的话,良率同样是难以保障的。

最后,我们看到在TSMC的版图中,有光源的封装,那么,光源怎么处理呢,是自己流片?还是第三方认证的流片呢?这是一只靴子了。光源和目前TSMC熟悉的CMOS工艺平台还是有比较大的差异的。但是,按照TSMC封装不支持第三方的组件来看,具体怎么操作,就要看台积电的决心了,呵呵。

5、tsmc的工作模式是什么?

既然介入硅光产业链,那么工作的模式就是下一个问题了。是开放PDK给第三方,如果不需要在平台上做一些特别的性能,PDK和实际的吻合程度比较高的话,那可能就真能实现像做电芯片那样,做光芯片,那么整个行业可能就会被颠覆了。

具体的实现方式,拭目以待,估计一年内就会揭开她的神秘的面纱了。

五、TSMC的iOIS带来了什么?

硅光封装平台iOIS会给我们带来什么呢?这是一个非常重要的问题

1、技术门槛下降

首先,光纤耦合的技术门槛门槛将下降,0.3dB的插损,这个目前在边耦合都难以达到的水平,通过光栅耦合竟然可以达到。而且可以实现光纤的可插拔/可拆卸,那么,光纤耦合需要的大量的人力节省下来了,同时,可靠性性也提升了。

其次,OE的EIC-PIC可以实现铜铜键合,那么,阻抗匹配、寄生参数、密度,以前困扰事情,都可以很好的解决了。OE将变成一个标准的组件,相对于直接调用。

最后,各种花式interposer的组合,设计工程师重点关注设计就好了,专业的事情,交给专业的人员。

2、测试转向自动化

wafer级的封装,需要wafer级的测试,将更多的是自动化的测试,尤其是耦合光栅的设计,自动化测试的成本和时间也会大大的缩短。

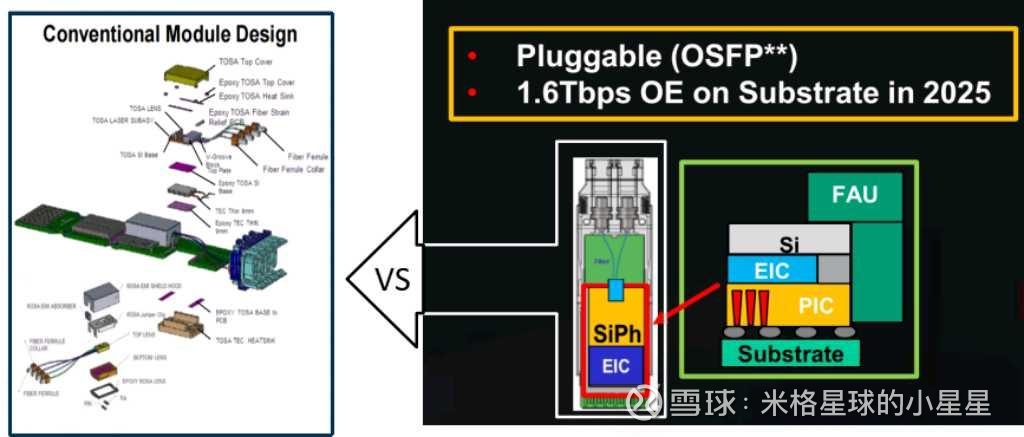

3、OE项目的产业链会发生重大的变化

对于台积在25年首推的iOIS平台来说,可插拔OE相关的产业链,可能会发生重大的变化。传统的大量分离元件的可插拔模块,会被高密度集成的芯片所替代。

4、FPP的技术资源逻辑在消失

从上面的描述可以看到,对于可插拔模块来说,技术人力资源的门槛在消失,传统可插拔光模块的配套的PIC、EIC、封装、耦合、测试等技术门槛和人力资源的门槛,可能会败给高密度集成的、自动化的平台。

传统FPP的三大支柱中的技术资源的支柱可能会动摇,进而造成产业生态的变化,例如,DC可以定制个性化的FPP模块等,降低成本,挤压光模块的利润空间。

5、CPO switch的OE相关的技术难度在下降

目前在CPO switch领域,能明确看到的是博通的bailly系列芯片和当下传闻很高的nvidia的quantum-X800。其它的几大switch公司则羞羞答答的半遮面,cisco目前明确的是25.6T的样机,marvell则一直是顾左右而言他,一定程度是CPO switch的产业的门槛比较高。cisco样机还是采用的尾纤方案,OE还是socket,先进性看不到博通的尾灯。以cisco的实力,确实有点奇怪。

如果TSMC能在iOIS上解决了耦合、封装,并开放PIC的pdk给第三方,则CPO switch的技术门槛大大降低。突然有个脑洞大开的想法,Cisco会是在和台积憋大招吗?呵呵。

六、奇点会是26年吗???

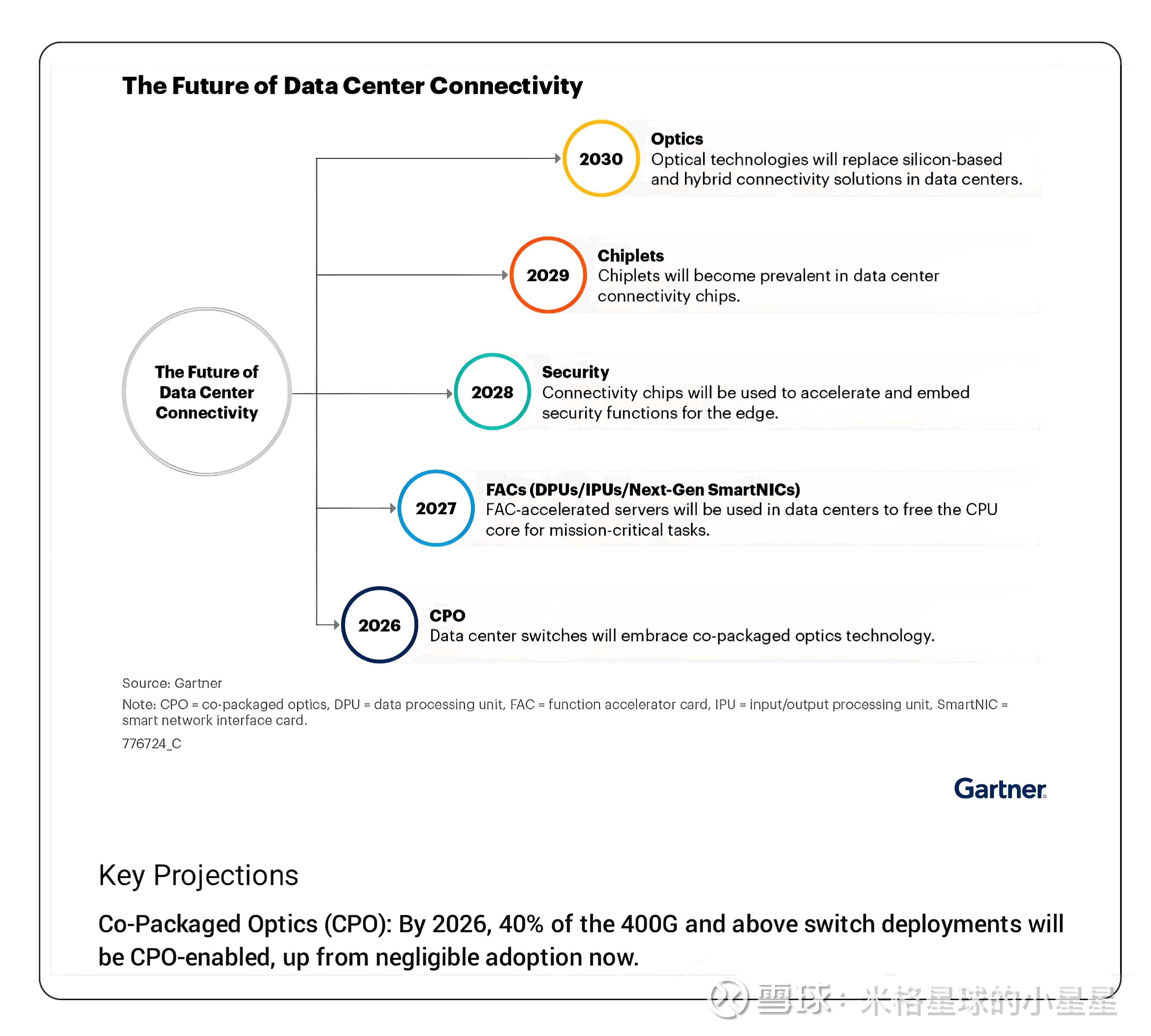

在今年深圳光博会的演讲中,CPO的风向突然变得诡异,一纵大咖调高了CPO switch的期望,gartner也调高了对于cpo switch的预测。

台积也透露了26年会在26年推出cpo switch,加之最近网上传闻很多的关于台积和英伟达、AMD的绯闻。看来26年确实是一个奇怪的时间点。

26年CPO switch会是一个奇点吗?为什么26年是一个特殊时间点?内在的逻辑是什么?敬请期待下集~