(原标题:CC扩产预期,北方华创和拓荆的ALD设备能做什么?)

简要:

1.High-K材料解决追求芯片尺寸变小与漏电之间的物理矛盾

2.引入High-K材料的核心工艺设备——ALD

3.High-K材料的三大技术优势

4.国内ALD厂商:北方华创与拓荆科技之间的竞争

5.设备三剑客:北方华创、中微、拓荆之间竞争与携手共进

6.延申思考:薄膜沉积设备成长路线与空间可能比刻蚀更大、更线性,设备厂第二名竞争还没未定论?

DRAM最基本的结构就是由一个晶体管(相当于开关)和一个电容(相当于储藏室)组成的单元。

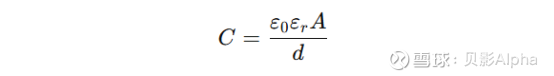

随着芯片尺寸不断缩小(从28纳米缩小到10纳米以下),电容这个的面积(A)急剧减小,但存储能力(电容值C)却不能降低。按照公式:

面积变小了,要维持容量,就只能减薄介质层厚度(d)。但传统硅氧化物(SiO?,介电常数ε_r≈3.9)一旦变得极薄(例如1纳米左右),漏电流就会指数级增加,导致电荷快速流失,数据无法稳定保存。

芯片尺寸缩小(A),与漏电流有着物理上的矛盾,因为引入High-K材料。

所以High-K材料就是介电常数ε_r较高的材料,High-K(高介电常数)材料,就是指介电常数(ε_r)比传统SiO?高数倍甚至十几倍的新材料,如氧化铪(HfO?,ε_r≈25)、氧化锆(ZrO?,ε_r≈30)等。

如果将电容比作“蓄水池”,则介电常数越高,对电子束缚能力加强,电子容量越高,不容易“渗漏”,即便把A面积造得更小,也仍能保持电容C,不必牺牲内壁厚度d。因此在DRAM制造工艺中,High-K材料非常关键。

那该材料是怎么沉积上去的呢?

主要有以下关键工艺:

1.选材与沉积工艺(ALD)

通过原子层沉积技术(Atomic Layer Deposition, ALD)精确沉积极薄均匀的高K薄膜。

2.界面优化工程

High-K材料与硅晶圆表面直接接触会产生缺陷(就像新粉刷的墙面不光滑),需用特殊处理工艺(例如氮化处理或加入极薄SiO?过渡层)修复这些缺陷,确保“墙面”光滑、平整,提高芯片性能与可靠性。

3.结合3D电容结构

此外,芯片设计师还将High-K材料与立体的圆柱或沟槽结构电容结合,大幅提升有效面积,使电容值进一步增强。

1.性能提升

因为High-K材料厚度更厚,电子“漏出”概率大幅降低,这有效延长了数据保存时间。同时,由于电容充放电效率更高,芯片数据读写速度也提升显著,可适用于更高频的DDR5、LPDDR5甚至未来的DDR6标准。

2.功耗降低

漏电减少,意味着不需要频繁刷新数据,直接降低芯片的动态功耗。同时,厚度增加意味着电场强度减小,也能有效降低静态功耗。

3.工艺兼容性强

现有芯片产线可较平稳地导入ALD沉积High-K材料的步骤,这对于先进制程(如10纳米以下)至关重要。

ALD则主要用于45nm及以下薄膜沉积工艺。ALD设备可实现芯片制造工艺中关键尺寸的精度控制,在结构复杂、薄膜厚度要求精准的先进逻辑IC、DRAM和NAND Flash中是必不可少的核心设备之一。

在ALD领域,拓荆科技与北方华创同样推出ALD设备。北方华创的ALD设备主要是Polaris A系列,可用于沉积氧化铝、氧化铪、氧化锆、氧化钛、TiN和AlN等多种薄膜的沉积(大多数其实就是所谓的High-K材料)。

拓荆科技在ALD领域国内领先,其产业化的FT-300T面向先进逻辑IC 28-14nmSADP、STI Liner工艺和55-40nm BSU工艺晶圆制造及2.5D/3D先进封装工艺中。不过值得注意的是公司的ALD设备是在PECVD核心技术上根据ALD反应原理,结合理论分析及仿真计算等创新设计而来,属于等离子体增强的ALD设备。公司在研的FT-300T Thermal-ALD设备用于28nm以下节点的氧化铝、AlN等多种金属化合物沉积;FT-300H则是面向12英寸 128层以上3D NAND和19/17nm DRAM存储芯片中氧化硅和SiN介质材料的沉积(也就是所谓的low K 材料,也可以用作栅极沉积)。

意思是就目前而言,在DRAM工艺中,华创的ALD主要用于high-K材料薄膜沉积,而拓荆科技的ALD可以用到栅极。假如某存储大厂扩产,那自然华创ALD需求会更高。

但是不得不承认拓荆的实力强劲:其中PECVD全面覆盖逻辑电路、DRAM存储、Flash闪存制造技术节点产线SiO2、SiN、SiON、BPSG和TEOS等多种通用介质材料薄膜沉积工序,并具备向更先进节点拓展的延伸性。目前国内主流晶圆厂均为公司客户。

拓荆的SACVD和PECVD,前者是国内唯一,后者也领先北方华创,但在高密度等离子体增强化学气相沉积(HDP-CVD)和低压化学气相沉积(LPCVD)等CVD设备上,北方华创也是国内的唯一,中微公司MOCVD设备则具备行业领先地位。目前单靠一家公司很难覆盖全部CVD设备,但拓荆科技与北方华创、中微公司三剑合璧,还是有望实现国产设备在CVD设备上的全覆盖,虽然目前这一目的还未实现。

在这里,不得不吐槽一下深圳某公司,在目前国内设备尚不能与国际大厂竞争的背景下,这家深圳公司筹集资金要什么都做,内卷国内厂商。

这家公司可能有无限的资金,也可以挖掘优秀人才。但是,既然实力那么强,就不能学习三剑客的“三剑合璧”、互补携手共进吗?直接攻打国外大厂好不好?

这是因为沉积工艺是要解决追求极致小尺寸,但是短沟道漏电可能性也在加大,小尺寸与漏电是个物理矛盾,有着很大的优化空间,多种设备配合、优化工艺。例如刚才说拓荆SACVD设备就可以起填补缺陷作用,在先进制程逻辑电路中,发挥很大作用。

而刻蚀领域,我们可以看到中微公布研发进展,是紧跟国际大厂最新工艺做的研发,例如GAA-Nano wire和Nano sheet工艺、甚至更先进的CFET工艺。这些是跟Fin FET(纵向刻蚀堆叠)不一样,GAA、CFET是横向堆叠,全新的工艺(后者CFET可能要2030年量产)。

如果中微能在国际大晶圆厂取得GAA的大订单,那也能迎来爆发。毕竟GAA和CFET需要high NA ***lithography,或许SMIC在新一代工艺突破要延后了。|

相比之下,沉积设备在解决小尺寸与漏电之间物理矛盾过程中,有着更线性的增长预期。(预告一下:必须得为精测电子正名,比中科飞测技术领先太多!!)

$北方华创(SZ002371)$ $中微公司(SH688012)$ $拓荆科技(SH688072)$